Join us at ISC24

To discuss integrating quantum computing into your existing compute infrastructure

With the rapid evolution of Quantum Computing, users are contemplating the best way to begin to integrate Quantum capabilities into their existing HPC and AI infrastructure. Find our experts at the ISC conference, May 12th-16th, in Hamburg, Germany to discuss our world leading hardware, applications, and case studies.

Exhibit Hall

Drop by Booth K50 in the exhibit hall to meet tour team and see a display of our System Model H2 chip, Powered by Honeywell.

If you’d like to schedule a 1:1 meeting, send us an email to schedule a time to meet. We have reserved meeting room Hall 5 at ISC, but we’d be happy to set up time to meet with you at or after the event.

Presentations

Our team will be presenting on a range of topics about integrating quantum computing into existing HPC infrastructure. They’ll be speaking about our hardware features and how you can leverage quantum computing with your existing HPC cluster.

May 13th

2:30pm – 3:00pm | Hall 4, ground level in the First-Time Exhibitor Pitch

Understanding Opportunities with Quantum Computing: Learn about our roadmap and key strategies to accelerate your current HPC clusters with the integration of quantum computing.

Presented by Nash Palaniswamy, Chief Commercial Officer, Quantinuum

May 14th

2:00pm – 2:30pm | GENCI Booth K40

Simulation of Transition Metal Oxide (TMO) Atomic Layer Deposition (ALD): A Study of the modelling of electronic energies used in the reactions involved for ALD of ZrO2 and of the reactivity of organometallic precursors used in ALD technology for controlling the quality of thin film deposition on different substrates. The study is a collaboration between C12 Quantum Electronics, Air Liquide and Quantinuum, with support from PAQ Ile de France.

Presented by Maud Einhorn, Technical Account Manager, and Gabriela Cimpan, Partner Manager, Quantinuum

May 14th

2:20pm – 2:35pm | Hall Z – 3rd floor

The Trapped-Ion Quantum Processors at Quantinuum: Quantinuum has constructed two generations of QCCD (quantum charge-coupled device) quantum processors. These processors use trapped-ions for qubits and sympathetic cooling, and shuttling operations to achieve high-fidelity gating operations on individual qubits and between any pair of qubits – making them fully-connected. In this talk, Dave will discuss Quantinuum’s efforts to rigorously benchmark the performance of these machines, highlighting their strengths and weaknesses. He’ll also give a brief survey of our efforts toward near-term quantum advantage and quantum error correction. Finally, he’ll sketch out some technological developments aimed at scaling these processors and the implications for future devices.

Presented by David Hayes, Sr. R&D Manager for Theory and Architecture

May 14th and May 15th

12:30pm – 1:00pm | Meeting Room Hall 5

3:30pm – 4:00pm | Meeting Room Hall 5

Quantum Computing, Error Correction, and Scaling for the Future at Quantinuum: Quantum computing promises to provide significant computational savings in valuable problems such as chemistry, materials, and cybersecurity. To make this a reality, errors in quantum operations must be suppressed significantly below where they are today, and the size of quantum computing hardware must be increased. Quantinuum has recently made significant strides in scaling to larger sizes. Join the session to hear about these exciting results, our plans to scale, and a look towards the future.

Presented by Chris Langer, Fellow and Chairman of the Technical Board, Quantinuum

May 16th

1:00pm – 1:20pm | Hall H, Booth L01 in the HPC Solutions Forum

Harnessing the potential of quantum computing: As the landscape of quantum computing continues to rapidly evolve, the question of when to invest in quantum computing knowledge remains a key strategic consideration for organizations. This talk will explore the challenge of quantum readiness by surveying some of the research collaborations Quantinuum has performed with a range of industry-leading organizations. Using real-world case studies, we will highlight the diverse array of sectors poised to benefit from early quantum adoption, including pharmaceuticals, finance, logistics, and cybersecurity. This talk begins to unpack why many first mover enterprise organizations have made significant investments in quantum readiness already, rather than deferring until the technology matures further.

Presented by Maud Einhorn, Technical Account Manager, Quantinuum

May 16th

4:30pm – 5:00pm | Hall Y1 - 2nd floor

Workshop on Benchmarking and Scaling the Quantum Charged Coupled Device Quantum Computing architecture in the Quantum and Hybrid Quantum-Classical Computing Approaches: The QCCD architecture provides a unique approach to quantum computing where qubits are mobile and operating zones are fixed. In contrast to QC architectures where qubit and couplings between them are fixed, the QCCD architecture naturally provides all-to-all connectivity and high-fidelity operations. Additional advanced features include mid-circuit measurement, qubit reset, conditional logic, and variable angle gates. The talk will present benchmarking of our machines and recent progress towards scaling to larger systems.

Presented by Chris Langer, Fellow and Chair of the Technical Board, Quantinuum

About Quantinuum

Quantinuum, the world’s largest integrated quantum company, pioneers powerful quantum computers and advanced software solutions. Quantinuum’s technology drives breakthroughs in materials discovery, cybersecurity, and next-gen quantum AI. With over 500 employees, including 370+ scientists and engineers, Quantinuum leads the quantum computing revolution across continents.

This month, Quantinuum welcomed its global user community to the first-ever Q-Net Connect, an annual forum designed to spark collaboration, share insights, and accelerate innovation across our full-stack quantum computing platforms. Over two days, users came together not only to learn from one another, but to build the relationships and momentum that we believe will help define the next chapter of quantum computing.

Q-Net Connect 2026 drew over 170 attendees from around the world to Denver, Colorado, including representatives from commercial enterprises and startups, academia and research institutions, and the public sector and non-profits - all users of Quantinuum systems.

The program was packed with inspiring keynotes, technical tracks, and customer presentations. Attendees heard from leaders at Quantinuum, as well as our partners at NVIDIA, JPMorganChase and BlueQubit; professors from the University of New Mexico, the University of Nottingham and Harvard University; national labs, including NIST, Oak Ridge National Laboratory, Sandia National Laboratories and Los Alamos National Laboratory; and other distinguished guests from across the global quantum ecosystem.

Congratulations to Q-Net Connect 2026 Award Recipients!

The mission of the Quantinuum Q-Net user community is to create a space for shared learning, collaboration and connection for those who adopt Quantinuum’s hardware, software and middleware platform. At this year’s Q-Net Connect, we awarded four organizations who made notable efforts to champion this effort.

- JPMorganChase received the ‘Guppy Adopter Award’ for their exemplary adoption of our quantum programming language, Guppy, in their research workflows.

- Phasecraft, a UK and US-based quantum algorithms startup, received the ‘Rising Star’ award for demonstrating exceptional early impact and advancing science using Quantinuum hardware, which they published in a December 2025 paper.

- Qedma, a quantum software startup, received the ‘Startup Partner Engagement’ award for their sustained engagement with Quantinuum platforms dating back to our first commercially deployed quantum computer, H1.

- Anna Dalmasso from the University of Nottingham received our ‘New Student Award’ for her impressive debut project on Quantinuum hardware and for delivering outstanding results as a new Q-Net student user.

Congratulations, again, and thank you to everyone who contributed to the success of the first Q-Net Connect!

Become a Q-Net Member

Q-Net offers year‑round support through user access, developer tools, documentation, trainings, webinars, and events. Members enjoy many exclusive benefits, including being the first to hear about exclusive content, publications and promotional offers.

By joining the community, you will be invited to exclusive gatherings to hear about the latest breakthroughs and connect with industry experts driving quantum innovation. Members also get access to Q‑Net Connect recordings and stay connected for future community updates.

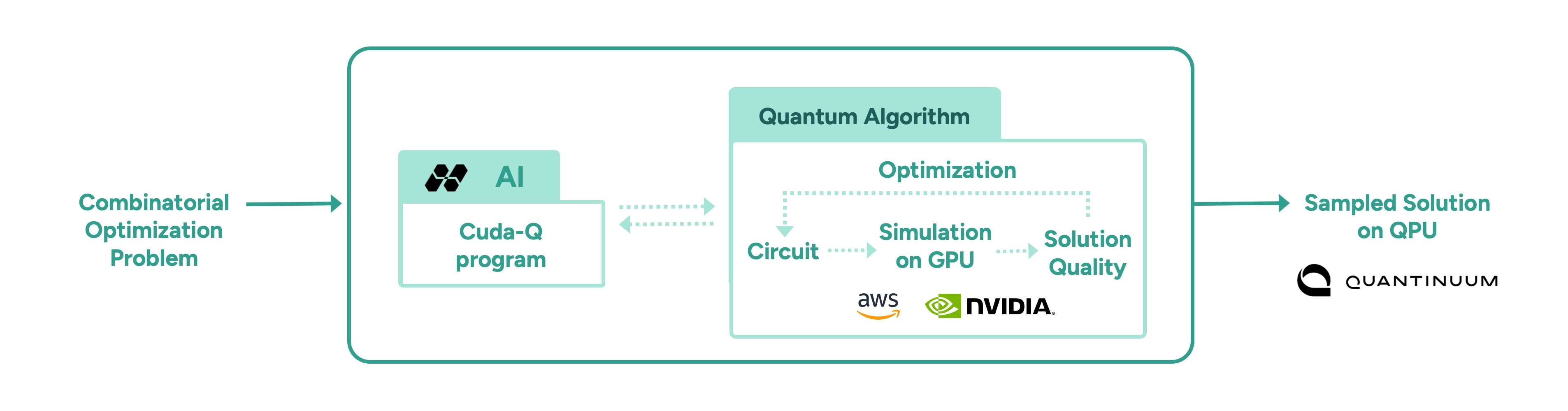

In a follow-up to our recent work with Hiverge using AI to discover algorithms for quantum chemistry, we’ve teamed up with Hiverge, Amazon Web Services (AWS) and NVIDIA to explore using AI to improve algorithms for combinatorial optimization.

With the rapid rise of Large Language Models (LLMs), people started asking “what if AI agents can serve as on-demand algorithm factories?” We have been working with Hiverge, an algorithm discovery company, AWS, and NVIDIA, to explore how LLMs can accelerate quantum computing research.

Hiverge – named for Hive, an AI that can develop algorithms – aims to make quantum algorithm design more accessible to researchers by translating high-level problem descriptions in mostly natural language into executable quantum circuits. The Hive takes the researcher’s initial sketch of an algorithm, as well as special constraints the researcher enumerates, and evolves it to a new algorithm that better meets the researcher’s needs. The output is expressed in terms of a familiar programming language, like Guppy or NVIDIA CUDA-Q, making it particularly easy to implement.

The AI is called a “Hive” because it is a collective of LLM agents, all of whom are editing the same codebase. In this work, the Hive was made up of LLM powerhouses such as Gemini, ChatGPT, Claude, Llama, as well as NVIDIA Nemotron, which was accessed through AWS’ Amazon Bedrock service. Many models are included because researchers know that diversity is a strength – just like a team of human researchers working in a group, a variety of perspectives often leads to the strongest result.

Once the LLMs are assembled, the Hive calls on them to do the work writing the desired algorithm; no new training is required. The algorithms are then executed and their ‘fitness’ (how well they solve the problem) is measured. Unfit programs do not survive, while the fittest ones evolve to the next generation. This process repeats, much like the evolutionary process of nature itself.

After evolution, the fittest algorithm is selected by the researchers and tested on other instances of the problem. This is a crucial step as the researchers want to understand how well it can generalize.

In this most recent work, the joint team explored how AI can assist in the discovery of heuristic quantum optimization algorithms, a class of algorithms aimed at improving efficiency across critical workstreams. These span challenges like optimal power grid dispatch and storage placement, arranging fuel inside nuclear reactors, and molecular design and reaction pathway optimization in drug, material, and chemical discovery—where solutions could translate into maximizing operational efficiency, dramatic reduction in costs, and rapid acceleration in innovation.

In other AI approaches, such as reinforcement learning, models are trained to solve a problem, but the resulting "algorithm" is effectively ‘hidden’ within a neural network. Here, the algorithm is written in Guppy or CUDA-Q (or Python), making it human-interpretable and easier to deploy on new problem instances.

This work leveraged the NVIDIA CUDA-Q platform, running on powerful NVIDIA GPUs made accessible by AWS. It’s state-of-the art accelerated computing was crucial; the research explored highly complex problems, challenges that lie at the edge of classical computing capacity. Before running anything on Quantinuum’s quantum computer, the researchers first used NVIDIA accelerated computing to simulate the quantum algorithms and assess their fitness. Once a promising algorithm is discovered, it could then be deployed on quantum hardware, creating an exciting new approach for scaling quantum algorithm design.

More broadly, this work points to one of many ways in which classical compute, AI, and quantum computing are most powerful in symbiosis. AI can be used to improve quantum, as demonstrated here, just as quantum can be used to extend AI. Looking ahead, we envision AI evolving programs that express a combination of algorithmic primitives, much like human mathematicians, such as Peter Shor and Lov Grover, have done. After all, both humans and AI can learn from each other.

As quantum computing power grows, so does the difficulty of error correction. Meeting that demand requires tight integration with high-performance classical computing, which is why we’ve partnered with NVIDIA to push the boundaries of real-time decoding performance.

Realizing the full power of quantum computing requires more than just qubits, it requires error rates low enough to run meaningful algorithms at scale. Physical qubits are sensitive to noise, which limits their capacity to handle calculations beyond a certain scale. To move beyond these limits, physical qubits must be combined into logical qubits, with errors continuously detected and corrected in real time before they can propagate and corrupt the calculation. This approach, known as fault tolerance, is a foundational requirement for any quantum computer intended to solve problems of real-world significance.

Part of the challenge of fault tolerance is the computational complexity of correcting errors in real time. Doing so involves sending the error syndrome data to a classical co-processor, solving a complex mathematical problem on that processor, then sending the resulting correction back to the quantum processor - all fast enough that it doesn’t slow down the quantum computation. For this reason, Quantum Error Correction (QEC) is currently one of the most demanding use-cases for tight coupling between classical and quantum computing.

Given the difficulty of the task, we have partnered with NVIDIA, leaders in accelerated computing. With the help of NVIDIA’s ultra-fast GPUs (and the GPU-accelerated BP-OSD decoder developed by NVIDIA as part of NVIDIA CUDA-Q QEC library), we were able to demonstrate real-time decoding of Helios’ qubits, all in a system that can be connected directly to our quantum processors using NVIDIA NVQLink.

While real-time decoding has been demonstrated before (notably, by our own scientists in this study), previous demonstrations were limited in their scalability and complexity.

In this demonstration, we used Brings’ code, a high-rate code that is possible with our all-to-all connectivity, to encode our physical qubits into noise-resilient logical qubits. Once we had them encoded, we ran gates as well as let them idle to see if we could catch and correct errors quickly and efficiently. We submitted the circuits via both NVIDIA CUDA-Q as well as our own Guppy language, underlining our commitment to accessible, ecosystem-friendly quantum computing.

The results were excellent: we were able to perform low-latency decoding that returned results in the time we needed, even for the faster clock cycles that we expect in future generation machines.

A key part of the achievement here is that we performed something called “correlated” decoding. In correlated decoding, you offload work that would normally be performed on the QPU onto the classical decoder. This is because, in ‘standard’ decoding, as you improve your error correction capabilities, it takes more and more time on the QPU. Correlated decoding elides this cost, saving QPU time for the tasks that only the quantum computer can do.

Stay tuned for our forthcoming paper with all the details.