Quantinuum Launches the Most Benchmarked Quantum Computer in the World and Publishes All the Data

New H2-1 shows strong performance across 15 benchmarks while expanding to 32 qubits and reaching a new Quantum Volume record of 65,536

Quantinuum’s new H2-1 quantum computer proves that trapped-ion architecture, which is well-known for achieving outstanding qubit quality and gate fidelity, is also built for scale – and Quantinuum’s benchmarking team has the data to prove it.

The bottom line: the new System Model H2 surpasses the H1 in complexity and qubit capacity while maintaining all the capabilities and fidelities of the previous generation – an astounding accomplishment when developing successive generations of quantum systems.

The newest entry in the H-Series is starting off with 32 qubits whereas H1 started with 10. H1 underwent several upgrades, ultimately reaching a 20-qubit capacity, and H2 is poised to pick up the torch and run with it. Staying true to the ultimate goal of increasing performance, H2 does not simply increase the qubit count but has already achieved a higher Quantum Volume than any other quantum computer ever built: 216 or 65,536.

Most importantly for the growing number of industrials and academic research institutions using the H-Series, benchmarking data shows that none of these hardware changes reduced the high-performance levels achieved by the System Model H1. That’s a key challenge in scaling quantum computers – preserving performance while adding qubits. The error rate on the fully connected circuits is comparable to the H1, even with a significant increase in qubits. Indeed, H2 exceeds H1 in multiple performance metrics: single-qubit gate error, two-qubit gate error, measurement cross talk and SPAM.

Key to the engineering advances made in the second-generation H-Series quantum computer are reductions in the physical resources required per qubit. To get the most out of the quantum charge-coupled device (QCCD) architecture, which the H-Series is built on, the hardware team at Quantinuum introduced a series of component innovations, to eliminate some performance limitations of the first generation in areas such as ion-loading, voltage sources, and delivering high-precision radio signals to control and manipulate ions.

The research paper, “A Race Track Trapped-Ion Quantum Processor,” details all of these engineering advances, and exactly what impacts they have on the computing performance of the machine. The paper includes results from component and system-level benchmarking tests that document the new machine’s capabilities at launch. These benchmarking metrics, combined with the company’s advances in topological qubits, represent a new phase of quantum computing.

Advancing Beyond Classical Simulation

In addition to the expanded capabilities, the new design provides operational efficiencies and a clear growth path.

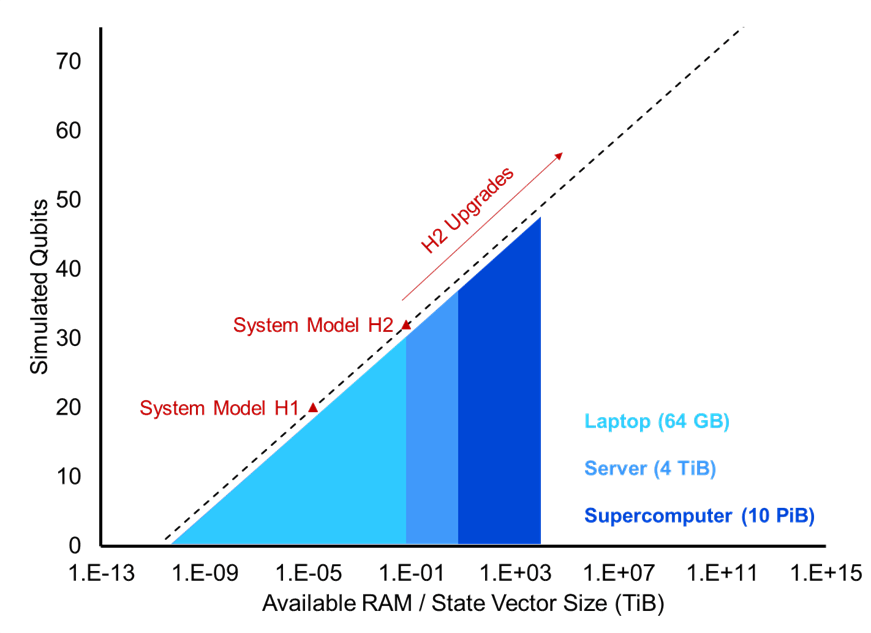

At launch, H2’s operations can still be emulated classically. However, Quantinuum released H2 at a small percentage of its full capacity. This new machine has the ability to upgrade to more qubits and gate zones, pushing it past the level where classical computers can hope to keep up.

Increased Efficiency in New Trap Design

This new generation quantum processor represents the first major trap upgrade in the H-Series. One of the most significant changes is the new oval (or racetrack) shape of the ion trap itself, which allows for a more efficient use of space and electrical control signals.

One key engineering challenge presented by this new design was the ability to route signals beneath the top metal layer of the trap. The hardware team addressed this by using radiofrequency (RF) tunnels. These tunnels allow inner and outer voltage electrodes to be implemented without being directly connected on the top surface of the trap, which is the key to making truly two-dimensional traps that will greatly increase the computational speed of these machines.

The new trap also features voltage “broadcasting,” which saves control signals by tying multiple DC electrodes within the trap to the same external signal. This is accomplished in “conveyor belt” regions on each side of the trap where ions are stored, improving electrode control efficiency by requiring only three voltage signals for 20 wells on each side of the trap.

The other significant component of H2 is the Magneto Optical Trap (MOT) which replaces the effusive atomic oven that H1 used. The MOT reduces the startup time for H2 by cooling the neutral atoms before shooting them at the trap, which will be crucial for very large machines that use large numbers of qubits.

Industry-leading Results from 15 Benchmarking Tests

Quantinuum has always valued transparency and supported its performance claims with publicly available data.

To quantify the impact of these hardware and design improvements, Quantinuum ran 15 tests that measured component operations, overall system performance and application performance. The complete results from the tests are included in the new research paper.

The hardware team ran four system-level benchmark tests that included more complex, multi-qubit circuits to give a broader picture of overall performance. These tests were:

- Mirror benchmarking: A scalable way to benchmark arbitrary quantum circuits.

- Quantum volume: A popular system-level test with a well-established construction that is comparable across gate-based quantum computers.

- Random circuit sampling: A computational task of sampling the output distributions of random quantum circuits.

- Entanglement certification in Greenberger-Horne-Zeilinger (GHZ) states: A demanding test of qubit coherence that is widely measured and reported across a variety of quantum hardware.

H2 showed state-of-the-art performance on each of these system-level tests, but the results of the GHZ test were particularly impressive. The verification of the globally entangled GHZ state requires a relatively high fidelity, which becomes harder and harder to achieve with larger numbers of qubits.

With H2’s 32 qubits and precision control of the environment in the ion trap, Quantinuum researchers were able to achieve an entangled state of 32 qubits with a fidelity of 82.0(7)%, setting a new world record.

In addition to the system level tests, the Quantinuum hardware team ran these component benchmark tests:

- SPAM experiment

- Single-qubit gate randomized benchmarking

- Two-qubit gate randomized benchmarking

- Two-qubit SU gate randomized benchmarking RB

- Two-qubit parameterized gate randomized benchmarking

- Measurement/reset crosstalk benchmarking

- Interleaved transport randomized benchmarking

The paper includes results from those tests as well as results from these application benchmarks:

- Hamiltonian simulation

- Quantum Approximate Optimization Algorithm

- Error correction: repetition code

- Holographic quantum dynamics simulation

About Quantinuum

Quantinuum, the world’s largest integrated quantum company, pioneers powerful quantum computers and advanced software solutions. Quantinuum’s technology drives breakthroughs in materials discovery, cybersecurity, and next-gen quantum AI. With over 500 employees, including 370+ scientists and engineers, Quantinuum leads the quantum computing revolution across continents.

- University of Southern Denmark (SDU) to use Quantinuum Helios, supported by the Danish e-Infrastructure Consortium (DeiC)

- Access to Helios enables SDU to test and refine fault-tolerant algorithms and error-correction codes under realistic hardware conditions

- The collaboration supports at a scale of 48 logical qubits, positioning Denmark at the forefront of scalable, practical quantum computing

- Researchers exploring the scientific foundations for future development of applications in fields including pharmaceuticals, finance, and defense

Progress in quantum computing is measured by hardware advances plus the algorithms and quantum error-correction codes that turn quantum systems into useful computational tools.

Thanks to recent hardware advances, researchers are increasingly sharpening their tools to probe the performance of quantum algorithms and understand how they behave in realistic conditions – where stability, system architecture and algorithm design all shape performance.

A new Denmark-based collaboration between the University of Southern Denmark (SDU), Quantinuum, and the Danish e-Infrastructure Consortium (DeiC) will utilize Quantinuum Helios. Researchers at the SDU’s Centre for Quantum Mathematics, led by Jørgen Ellegaard Andersen, will use Helios to pursue research into topological quantum computing.

Their work could help explain how and why successful quantum algorithms perform as they do, informing the development of high-performance algorithms suited to emerging quantum systems. They’re exploring the scientific foundations that support future quantum applications across areas including pharmaceuticals, finance, and defense.

“We are thrilled to gain access to Quantinuum’s high-fidelity Helios system. This collaboration gives us a unique opportunity to test the limits of our algorithms and evaluate system performance, while advancing fundamental research and laying the foundation for future applications.”

— Professor Jørgen Ellegaard Andersen, Director of the Centre for Quantum Mathematics at University of Southern Denmark

Why topological methods matter

Topological quantum computing is an area of research that connects quantum computation with deep mathematical structures. It includes the study of error correcting codes known as surface codes that encode quantum information in the global properties of systems of logical qubits.

The research team will explore how these codes behave, and how they may support the development of fault-tolerant quantum algorithms in practical implementations under realistic conditions.

This distinction between theory and practical implementation matters. In theory, topological approaches offer a rich framework for designing algorithms and error-correcting codes. In practice, researchers need to understand how those ideas perform when implemented on real systems, where questions of noise, stability, overhead, and scaling become central. The collaboration will allow the SDU team to investigate these questions directly.

New ways to benchmark quantum processors

Beyond individual algorithms and codes, the research will also develop tools for benchmarking quantum processors. The goal is to develop new ways to characterize fidelity and stability in regimes that can be difficult to access.

The team will also explore hybrid quantum–classical approaches, including machine-learning techniques assisted by quantum hardware, to study the mathematical structures at the heart of topological quantum computing. This work reflects a broader field of research in which quantum and classical methods are used together, each contributing to parts of a computational problem.

Strengthening Denmark’s quantum ecosystem

The collaboration reflects the growing role of national quantum infrastructure in supporting research and talent development. Denmark has a long tradition of scientific innovation, and this collaboration is intended to support the country’s continued development in quantum technology.

The initiative is supported by DeiC, which played a central role in securing funding and enabling access to Quantinuum’s systems. DeiC has been assigned a particular role in developing and coordinating quantum infrastructure initiatives for the benefit of universities and industry, operating without its own commercial, sectoral, or geographical interests. This includes securing dedicated access to quantum computers, producing advisory services and supporting the development of new talent in the Danish quantum sector.

“DeiC’s special effort to secure funding and access for this research initiative is rooted in our organization’s role in relation to the Danish Government’s strategy for quantum technology.”

— Henrik Navntoft Sønderskov, Head of Quantum at Danish e-Infrastructure Consortium

This collaboration promises to accelerate the development of practical algorithms. It is grounded in fundamental science – but its focus is practical: discovering and testing mathematical approaches to topological quantum computing that can be implemented, evaluated, and improved on real quantum hardware.

That work requires both theoretical insight and access to a system such as Helios capable of supporting meaningful scientific work.

This month, Quantinuum welcomed its global user community to the first-ever Q-Net Connect, an annual forum designed to spark collaboration, share insights, and accelerate innovation across our full-stack quantum computing platforms. Over two days, users came together not only to learn from one another, but to build the relationships and momentum that we believe will help define the next chapter of quantum computing.

Q-Net Connect 2026 drew over 170 attendees from around the world to Denver, Colorado, including representatives from commercial enterprises and startups, academia and research institutions, and the public sector and non-profits - all users of Quantinuum systems.

The program was packed with inspiring keynotes, technical tracks, and customer presentations. Attendees heard from leaders at Quantinuum, as well as our partners at NVIDIA, JPMorganChase and BlueQubit; professors from the University of New Mexico, the University of Nottingham and Harvard University; national labs, including NIST, Oak Ridge National Laboratory, Sandia National Laboratories and Los Alamos National Laboratory; and other distinguished guests from across the global quantum ecosystem.

Congratulations to Q-Net Connect 2026 Award Recipients!

The mission of the Quantinuum Q-Net user community is to create a space for shared learning, collaboration and connection for those who adopt Quantinuum’s hardware, software and middleware platform. At this year’s Q-Net Connect, we awarded four organizations who made notable efforts to champion this effort.

- JPMorganChase received the ‘Guppy Adopter Award’ for their exemplary adoption of our quantum programming language, Guppy, in their research workflows.

- Phasecraft, a UK and US-based quantum algorithms startup, received the ‘Rising Star’ award for demonstrating exceptional early impact and advancing science using Quantinuum hardware, which they published in a December 2025 paper.

- Qedma, a quantum software startup, received the ‘Startup Partner Engagement’ award for their sustained engagement with Quantinuum platforms dating back to our first commercially deployed quantum computer, H1.

- Anna Dalmasso from the University of Nottingham received our ‘New Student Award’ for her impressive debut project on Quantinuum hardware and for delivering outstanding results as a new Q-Net student user.

Congratulations, again, and thank you to everyone who contributed to the success of the first Q-Net Connect!

Become a Q-Net Member

Q-Net offers year‑round support through user access, developer tools, documentation, trainings, webinars, and events. Members enjoy many exclusive benefits, including being the first to hear about exclusive content, publications and promotional offers.

By joining the community, you will be invited to exclusive gatherings to hear about the latest breakthroughs and connect with industry experts driving quantum innovation. Members also get access to Q‑Net Connect recordings and stay connected for future community updates.

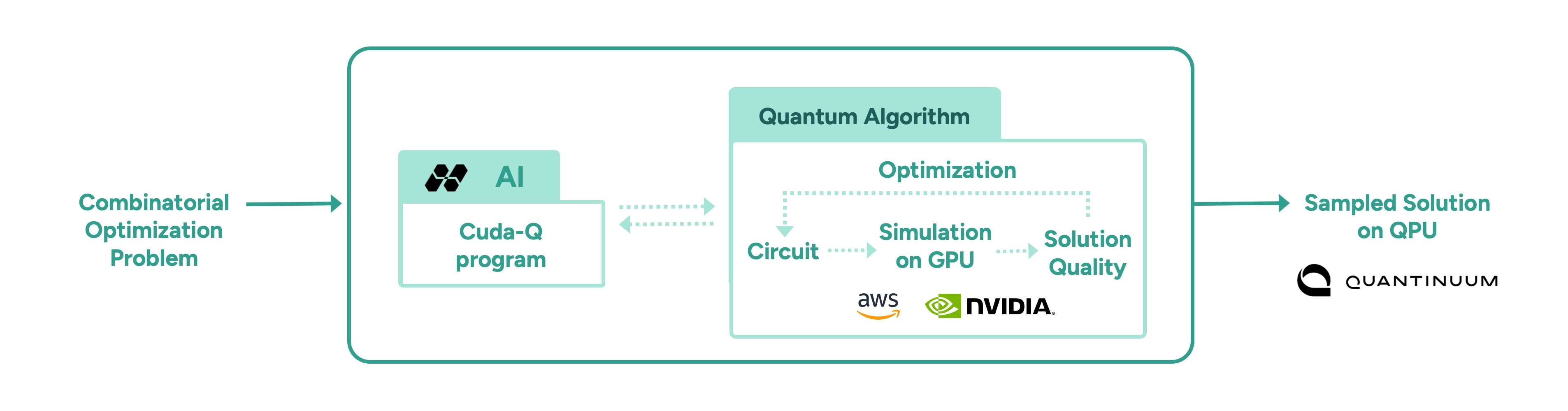

In a follow-up to our recent work with Hiverge using AI to discover algorithms for quantum chemistry, we’ve teamed up with Hiverge, Amazon Web Services (AWS) and NVIDIA to explore using AI to improve algorithms for combinatorial optimization.

With the rapid rise of Large Language Models (LLMs), people started asking “what if AI agents can serve as on-demand algorithm factories?” We have been working with Hiverge, an algorithm discovery company, AWS, and NVIDIA, to explore how LLMs can accelerate quantum computing research.

Hiverge – named for Hive, an AI that can develop algorithms – aims to make quantum algorithm design more accessible to researchers by translating high-level problem descriptions in mostly natural language into executable quantum circuits. The Hive takes the researcher’s initial sketch of an algorithm, as well as special constraints the researcher enumerates, and evolves it to a new algorithm that better meets the researcher’s needs. The output is expressed in terms of a familiar programming language, like Guppy or NVIDIA CUDA-Q, making it particularly easy to implement.

The AI is called a “Hive” because it is a collective of LLM agents, all of whom are editing the same codebase. In this work, the Hive was made up of LLM powerhouses such as Gemini, ChatGPT, Claude, Llama, as well as NVIDIA Nemotron, which was accessed through AWS’ Amazon Bedrock service. Many models are included because researchers know that diversity is a strength – just like a team of human researchers working in a group, a variety of perspectives often leads to the strongest result.

Once the LLMs are assembled, the Hive calls on them to do the work writing the desired algorithm; no new training is required. The algorithms are then executed and their ‘fitness’ (how well they solve the problem) is measured. Unfit programs do not survive, while the fittest ones evolve to the next generation. This process repeats, much like the evolutionary process of nature itself.

After evolution, the fittest algorithm is selected by the researchers and tested on other instances of the problem. This is a crucial step as the researchers want to understand how well it can generalize.

In this most recent work, the joint team explored how AI can assist in the discovery of heuristic quantum optimization algorithms, a class of algorithms aimed at improving efficiency across critical workstreams. These span challenges like optimal power grid dispatch and storage placement, arranging fuel inside nuclear reactors, and molecular design and reaction pathway optimization in drug, material, and chemical discovery—where solutions could translate into maximizing operational efficiency, dramatic reduction in costs, and rapid acceleration in innovation.

In other AI approaches, such as reinforcement learning, models are trained to solve a problem, but the resulting "algorithm" is effectively ‘hidden’ within a neural network. Here, the algorithm is written in Guppy or CUDA-Q (or Python), making it human-interpretable and easier to deploy on new problem instances.

This work leveraged the NVIDIA CUDA-Q platform, running on powerful NVIDIA GPUs made accessible by AWS. It’s state-of-the art accelerated computing was crucial; the research explored highly complex problems, challenges that lie at the edge of classical computing capacity. Before running anything on Quantinuum’s quantum computer, the researchers first used NVIDIA accelerated computing to simulate the quantum algorithms and assess their fitness. Once a promising algorithm is discovered, it could then be deployed on quantum hardware, creating an exciting new approach for scaling quantum algorithm design.

More broadly, this work points to one of many ways in which classical compute, AI, and quantum computing are most powerful in symbiosis. AI can be used to improve quantum, as demonstrated here, just as quantum can be used to extend AI. Looking ahead, we envision AI evolving programs that express a combination of algorithmic primitives, much like human mathematicians, such as Peter Shor and Lov Grover, have done. After all, both humans and AI can learn from each other.