IEEE Quantum Week 2025

Every year, The IEEE International Conference on Quantum Computing and Engineering – or IEEE Quantum Week – brings together engineers, scientists, researchers, students, and others to learn about advancements in quantum computing.

This year’s conference from August 31st – September 5th, is being held in Albuquerque, New Mexico, a burgeoning epicenter for quantum technology innovation and the home to our new location that will support ongoing collaborative efforts to advance the photonics technologies critical to furthering our product development.

Throughout IEEE Quantum Week, our quantum experts will be on-site to share insights on upgrades to our hardware, enhancements to our software stack, our path to error correction, and more.

Meet our team at Booth #507 and join the below sessions to discover how Quantinuum is forging the path to fault-tolerant quantum computing with our integrated full-stack.

September 2nd

Quantum Software Workshop

Quantum Software 2.1: Open Problems, New Ideas, and Paths to Scale

1:15 – 2:10pm MDT | Mesilla

We recently shared the details of our new software stack for our next-generation systems, including Helios (launching in 2025). Quantinuum’s Agustín Borgna will deliver a lighting talk to introduce Guppy, our new, open-source programming language based on Python, one of the most popular general-use programming languages for classical computing.

September 3rd

PAN08: Progress and Platforms in the Era of Reliable Quantum Computing

1:00 – 2:30pm MDT | Apache

We are entering the era of reliable quantum computing. Across the industry, quantum hardware and software innovators are enabling this transformation by creating reliable logical qubits and building integrated technology stacks that span the application layer, middleware and hardware. Attendees will hear about current and near-term developments from Microsoft, Quantinuum and Atom Computing. They will also gain insights into challenges and potential solutions from across the ecosystem, learn about Microsoft’s qubit-virtualization system, and get a peek into future developments from Quantinuum and Microsoft.

BOF03: Exploring Distributed Quantum Simulators on Exa-scale HPC Systems

3:00 – 4:30pm MDT | Apache

The core agenda of the session is dedicated to addressing key technical and collaborative challenges in this rapidly evolving field. Discussions will concentrate on innovative algorithm design tailored for HPC environments, the development of sophisticated hybrid frameworks that seamlessly combine classical and quantum computational resources, and the crucial task of establishing robust performance benchmarks on large-scale CPU/GPU HPC infrastructures.

September 4th

PAN11: Real-time Quantum Error Correction: Achievements and Challenges

1:00 – 2:30pm MDT | La Cienega

This panel will explore the current state of real-time quantum error correction, identifying key challenges and opportunities as we move toward large-scale, fault-tolerant systems. Real-time decoding is a multi-layered challenge involving algorithms, software, compilation, and computational hardware that must work in tandem to meet the speed, accuracy, and scalability demands of FTQC. We will examine how these challenges manifest for multi-logical qubit operations, and discuss steps needed to extend the decoding infrastructure from intermediate-scale systems to full-scale quantum processors.

September 5th

Keynote by NVIDIA

8:00 – 9:30am MDT | Kiva Auditorium

During his keynote talk, NVIDIA’s Head of Quantum Computing Product, Sam Stanwyck, will detail our partnership to fast-track commercially scalable quantum supercomputers. Discover how Quantinuum and NVIDIA are pushing the boundaries to deliver on the power of hybrid quantum and classical compute – from integrating NVIDIA’s CUDA-Q Platform with access to Quantinuum’s industry-leading hardware to the recently announced NVIDIA Quantum Research Center (NVAQC).

Featured Research at the IEEE Poster Session:

Visible Photonic Component Development for Trapped-Ion Quantum Computing

September 2nd from 6:30 - 8:00pm MDT | September 3rd from 9:30 - 10:00am MDT | September 4th from 11:30 - 12:30pm MDT

Authors: Elliot Lehman, Molly Krogstad, Molly P. Andersen, Sara Cambell, Kirk Cook, Bryan DeBono, Christopher Ertsgaard, Azure Hansen, Duc Nguyen, Adam Ollanik, Daniel Ouellette, Michael Plascak, Justin T. Schultz, Johanna Zultak, Nicholas Boynton, Christopher DeRose,Michael Gehl, and Nicholas Karl

Scaling Up Trapped-Ion Quantum Processors with Integrated Photonics

September 2nd from 6:30 - 8:00pm MDT and 2:30 - 3:00pm MDT | September 4th from 9:30 - 10:00am MDT

Authors: Molly Andersen, Bryan DeBono, Sara Campbell, Kirk Cook, David Gaudiosi, Christopher Ertsgaard, Azure Hansen, Todd Klein, Molly Krogstad, Elliot Lehman, Gregory MacCabe, Duc Nguyen, Nhung Nguyen, Adam Ollanik, Daniel Ouellette, Brendan Paver, Michael Plascak, Justin Schultz and Johanna Zultak

Research Collaborations with the Local Ecosystem

In a partnership that is part of a long-standing relationship with Los Alamos National Laboratory, we have been working on new methods to make quantum computing operations more efficient, and ultimately, scalable.

Learn more in our Research Paper: Classical shadows with symmetries

Our teams collaborated with Sandia National Laboratories demonstrating our leadership in benchmarking. In this paper, we implemented a technique devised by researchers at Sandia to measure errors in mid-circuit measurement and reset. Understanding these errors helps us to reduce them while helping our customers understand what to expect while using our hardware.

Learn more in our Research Paper: Measuring error rates of mid-circuit measurements

About Quantinuum

Quantinuum, the world’s largest integrated quantum company, pioneers powerful quantum computers and advanced software solutions. Quantinuum’s technology drives breakthroughs in materials discovery, cybersecurity, and next-gen quantum AI. With over 500 employees, including 370+ scientists and engineers, Quantinuum leads the quantum computing revolution across continents.

This month, Quantinuum welcomed its global user community to the first-ever Q-Net Connect, an annual forum designed to spark collaboration, share insights, and accelerate innovation across our full-stack quantum computing platforms. Over two days, users came together not only to learn from one another, but to build the relationships and momentum that we believe will help define the next chapter of quantum computing.

Q-Net Connect 2026 drew over 170 attendees from around the world to Denver, Colorado, including representatives from commercial enterprises and startups, academia and research institutions, and the public sector and non-profits - all users of Quantinuum systems.

The program was packed with inspiring keynotes, technical tracks, and customer presentations. Attendees heard from leaders at Quantinuum, as well as our partners at NVIDIA, JPMorganChase and BlueQubit; professors from the University of New Mexico, the University of Nottingham and Harvard University; national labs, including NIST, Oak Ridge National Laboratory, Sandia National Laboratories and Los Alamos National Laboratory; and other distinguished guests from across the global quantum ecosystem.

Congratulations to Q-Net Connect 2026 Award Recipients!

The mission of the Quantinuum Q-Net user community is to create a space for shared learning, collaboration and connection for those who adopt Quantinuum’s hardware, software and middleware platform. At this year’s Q-Net Connect, we awarded four organizations who made notable efforts to champion this effort.

- JPMorganChase received the ‘Guppy Adopter Award’ for their exemplary adoption of our quantum programming language, Guppy, in their research workflows.

- Phasecraft, a UK and US-based quantum algorithms startup, received the ‘Rising Star’ award for demonstrating exceptional early impact and advancing science using Quantinuum hardware, which they published in a December 2025 paper.

- Qedma, a quantum software startup, received the ‘Startup Partner Engagement’ award for their sustained engagement with Quantinuum platforms dating back to our first commercially deployed quantum computer, H1.

- Anna Dalmasso from the University of Nottingham received our ‘New Student Award’ for her impressive debut project on Quantinuum hardware and for delivering outstanding results as a new Q-Net student user.

Congratulations, again, and thank you to everyone who contributed to the success of the first Q-Net Connect!

Become a Q-Net Member

Q-Net offers year‑round support through user access, developer tools, documentation, trainings, webinars, and events. Members enjoy many exclusive benefits, including being the first to hear about exclusive content, publications and promotional offers.

By joining the community, you will be invited to exclusive gatherings to hear about the latest breakthroughs and connect with industry experts driving quantum innovation. Members also get access to Q‑Net Connect recordings and stay connected for future community updates.

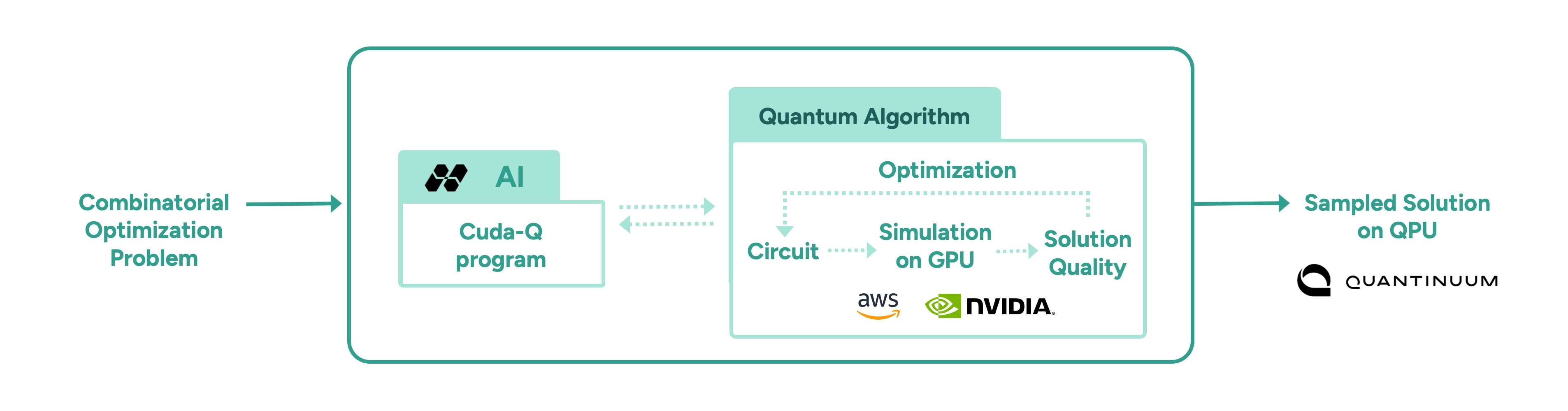

In a follow-up to our recent work with Hiverge using AI to discover algorithms for quantum chemistry, we’ve teamed up with Hiverge, Amazon Web Services (AWS) and NVIDIA to explore using AI to improve algorithms for combinatorial optimization.

With the rapid rise of Large Language Models (LLMs), people started asking “what if AI agents can serve as on-demand algorithm factories?” We have been working with Hiverge, an algorithm discovery company, AWS, and NVIDIA, to explore how LLMs can accelerate quantum computing research.

Hiverge – named for Hive, an AI that can develop algorithms – aims to make quantum algorithm design more accessible to researchers by translating high-level problem descriptions in mostly natural language into executable quantum circuits. The Hive takes the researcher’s initial sketch of an algorithm, as well as special constraints the researcher enumerates, and evolves it to a new algorithm that better meets the researcher’s needs. The output is expressed in terms of a familiar programming language, like Guppy or NVIDIA CUDA-Q, making it particularly easy to implement.

The AI is called a “Hive” because it is a collective of LLM agents, all of whom are editing the same codebase. In this work, the Hive was made up of LLM powerhouses such as Gemini, ChatGPT, Claude, Llama, as well as NVIDIA Nemotron, which was accessed through AWS’ Amazon Bedrock service. Many models are included because researchers know that diversity is a strength – just like a team of human researchers working in a group, a variety of perspectives often leads to the strongest result.

Once the LLMs are assembled, the Hive calls on them to do the work writing the desired algorithm; no new training is required. The algorithms are then executed and their ‘fitness’ (how well they solve the problem) is measured. Unfit programs do not survive, while the fittest ones evolve to the next generation. This process repeats, much like the evolutionary process of nature itself.

After evolution, the fittest algorithm is selected by the researchers and tested on other instances of the problem. This is a crucial step as the researchers want to understand how well it can generalize.

In this most recent work, the joint team explored how AI can assist in the discovery of heuristic quantum optimization algorithms, a class of algorithms aimed at improving efficiency across critical workstreams. These span challenges like optimal power grid dispatch and storage placement, arranging fuel inside nuclear reactors, and molecular design and reaction pathway optimization in drug, material, and chemical discovery—where solutions could translate into maximizing operational efficiency, dramatic reduction in costs, and rapid acceleration in innovation.

In other AI approaches, such as reinforcement learning, models are trained to solve a problem, but the resulting "algorithm" is effectively ‘hidden’ within a neural network. Here, the algorithm is written in Guppy or CUDA-Q (or Python), making it human-interpretable and easier to deploy on new problem instances.

This work leveraged the NVIDIA CUDA-Q platform, running on powerful NVIDIA GPUs made accessible by AWS. It’s state-of-the art accelerated computing was crucial; the research explored highly complex problems, challenges that lie at the edge of classical computing capacity. Before running anything on Quantinuum’s quantum computer, the researchers first used NVIDIA accelerated computing to simulate the quantum algorithms and assess their fitness. Once a promising algorithm is discovered, it could then be deployed on quantum hardware, creating an exciting new approach for scaling quantum algorithm design.

More broadly, this work points to one of many ways in which classical compute, AI, and quantum computing are most powerful in symbiosis. AI can be used to improve quantum, as demonstrated here, just as quantum can be used to extend AI. Looking ahead, we envision AI evolving programs that express a combination of algorithmic primitives, much like human mathematicians, such as Peter Shor and Lov Grover, have done. After all, both humans and AI can learn from each other.

As quantum computing power grows, so does the difficulty of error correction. Meeting that demand requires tight integration with high-performance classical computing, which is why we’ve partnered with NVIDIA to push the boundaries of real-time decoding performance.

Realizing the full power of quantum computing requires more than just qubits, it requires error rates low enough to run meaningful algorithms at scale. Physical qubits are sensitive to noise, which limits their capacity to handle calculations beyond a certain scale. To move beyond these limits, physical qubits must be combined into logical qubits, with errors continuously detected and corrected in real time before they can propagate and corrupt the calculation. This approach, known as fault tolerance, is a foundational requirement for any quantum computer intended to solve problems of real-world significance.

Part of the challenge of fault tolerance is the computational complexity of correcting errors in real time. Doing so involves sending the error syndrome data to a classical co-processor, solving a complex mathematical problem on that processor, then sending the resulting correction back to the quantum processor - all fast enough that it doesn’t slow down the quantum computation. For this reason, Quantum Error Correction (QEC) is currently one of the most demanding use-cases for tight coupling between classical and quantum computing.

Given the difficulty of the task, we have partnered with NVIDIA, leaders in accelerated computing. With the help of NVIDIA’s ultra-fast GPUs (and the GPU-accelerated BP-OSD decoder developed by NVIDIA as part of NVIDIA CUDA-Q QEC library), we were able to demonstrate real-time decoding of Helios’ qubits, all in a system that can be connected directly to our quantum processors using NVIDIA NVQLink.

While real-time decoding has been demonstrated before (notably, by our own scientists in this study), previous demonstrations were limited in their scalability and complexity.

In this demonstration, we used Brings’ code, a high-rate code that is possible with our all-to-all connectivity, to encode our physical qubits into noise-resilient logical qubits. Once we had them encoded, we ran gates as well as let them idle to see if we could catch and correct errors quickly and efficiently. We submitted the circuits via both NVIDIA CUDA-Q as well as our own Guppy language, underlining our commitment to accessible, ecosystem-friendly quantum computing.

The results were excellent: we were able to perform low-latency decoding that returned results in the time we needed, even for the faster clock cycles that we expect in future generation machines.

A key part of the achievement here is that we performed something called “correlated” decoding. In correlated decoding, you offload work that would normally be performed on the QPU onto the classical decoder. This is because, in ‘standard’ decoding, as you improve your error correction capabilities, it takes more and more time on the QPU. Correlated decoding elides this cost, saving QPU time for the tasks that only the quantum computer can do.

Stay tuned for our forthcoming paper with all the details.